Zynq-7000 – это система на кристалле, это абсолютно новый класс изделий от компании Xilinx. Zynq-7000 – это ПЛИС седьмого семейства с встроенным аппаратным ядром ARM. Подобная комбинация открывает широкие возможности, как для разработчиков аппаратного обеспечения на ПЛИС, так и для разработчиков программного обеспечения на ARM. За счет ресурсов ПЛИС обеспечивается лучшая производительность, а наличие аппаратного процессорного ядра ARM позволяет делать разработки более гибкими и универсальными.

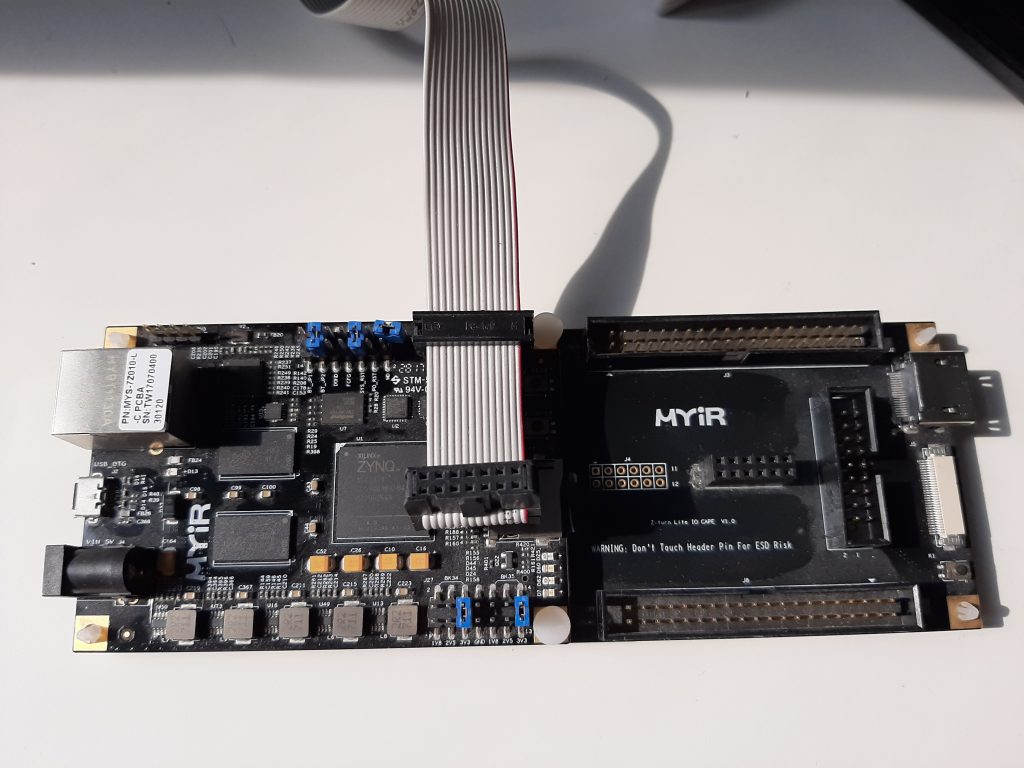

Технические характеристики Z-Turn Lite:

- SoC

- Xilinx XC7Z007S-1CLG400C (Zynq-7007S) с одиночным ядром ARM Cortex A9 @ 667 МГц, полотно Artix-7 FPGA с 23K логических ячеек, 14,400 LUTs, 66 DSP частей ИЛИ

- Xilinx XC7Z010-1CLG400C (Zynq-7010) с двумя ядрами ARM Cortex A9 @ 667 МГц, полотно Artix-7 FPGA с 28K логических ячеек, 17,600 LUTs, 80 DSP частей.

- Оперативная память – 512 Мб DDR3 SDRAM (2 x 256 Мб, 32-bit)

- Хранилище – 4 Гб eMMC флэш, 16 Мб QSPI флэш и слот micro SD

- Связь – 10/100/1000M Ethernet

- USB – 1x mini USB 2.0 OTG порт

- Отладка – USB-UART интерфейс отладки, 14-контактный JTAG интерфейс

- Пользовательский ввод/вывод –1x 120-контактный коннектор с шагом 0.5 мм для интерфейса расширения на обратной стороне платы

- Датчики – 3-осевой акселерометр и датчик температуры

- Прочее – 2x кнопки (сброс и пользовательская), перемычка переключения загрузки, 5x светодиодов, 1x зуммер

- Питание – 5 В/2 А через разъем питания типа «бочонок»

- Размеры – 91 x 63 мм (10-слойная печатная плата)

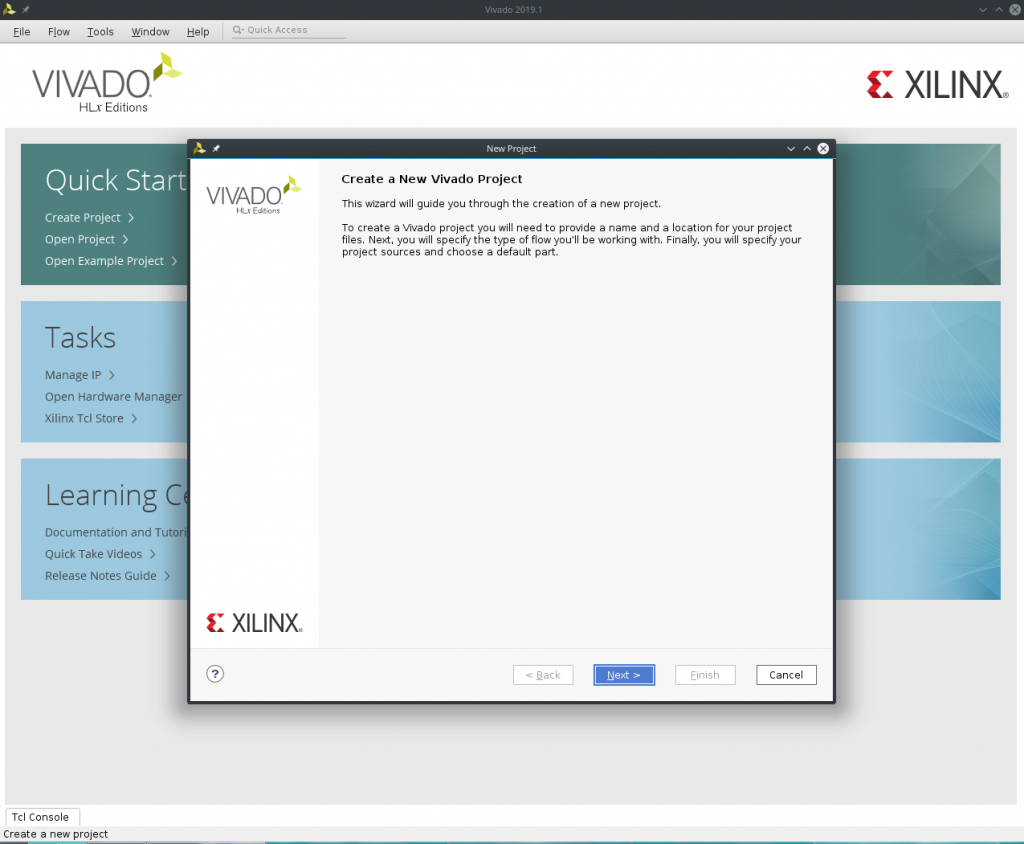

Создание проекта.

Создадим проект для отладочной платы в Xilinx Vivado (тут самое главное – нажимать правильные кнопки).

1. Создаем новый проект. Нажимаем далее.

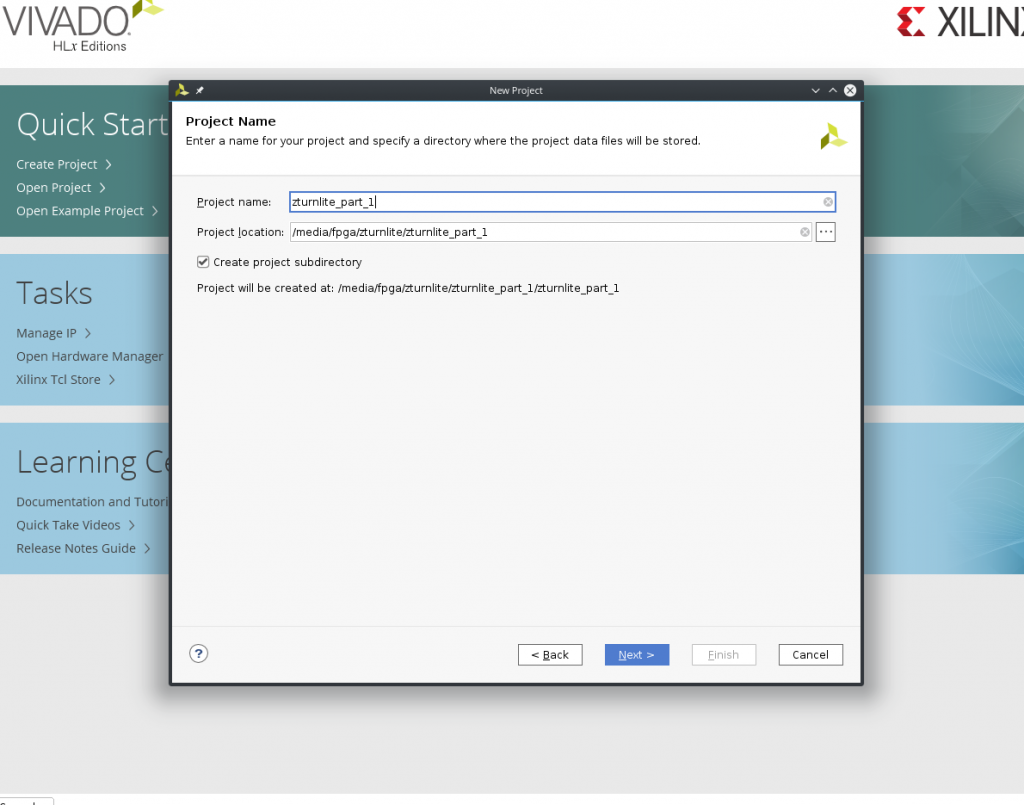

2. Вводим имя проекта и расположение проекта. Нажимаем далее.

3. Выбираем тип проекта. Нажимаем далее.

4. Окно добавление исходных файлов, у нас их нету для данного проекта, нажимаем далее.

5. Окно добавление файлов ограничения целостности, у нас их тоже нету для данного проекта, нажимаем далее.

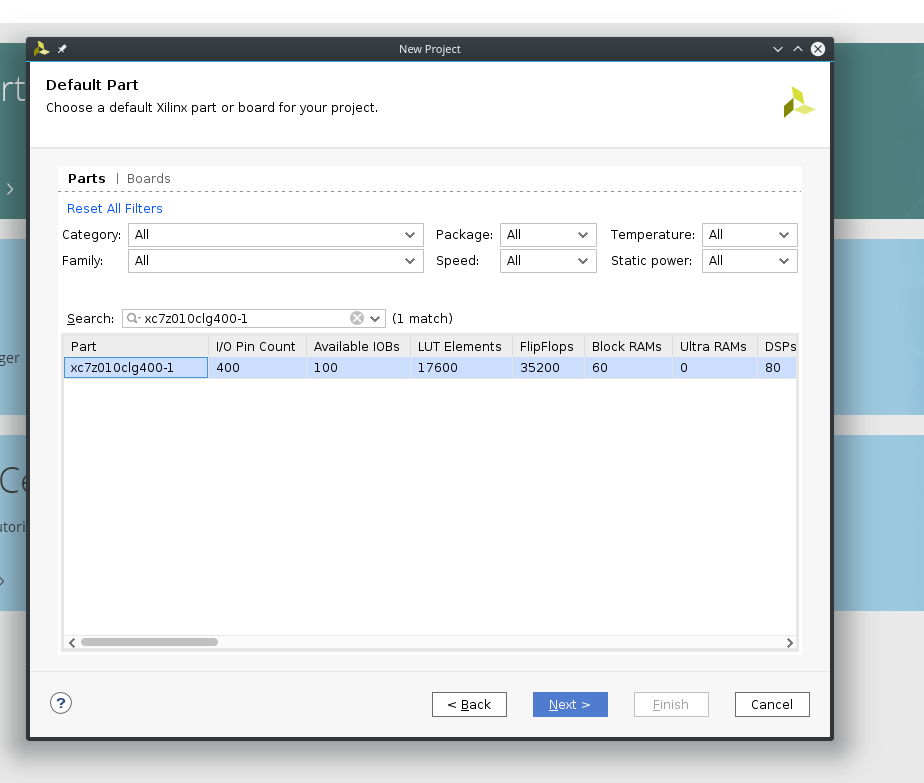

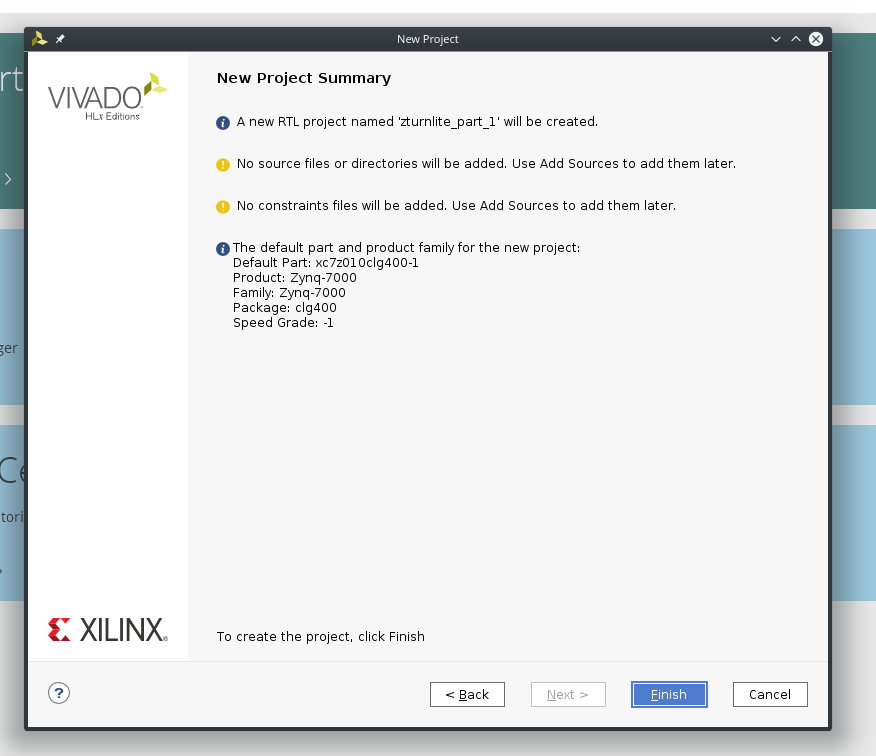

6. Выбираем нужный нам soc, как на картинке и наживаем далее.

7. Проект сконфигурирован, нажимаем закончить.

8. Нажимаем создать блок дизайн (Create Block Design). С лева в меню IP INTEGRATOR. Появляется меню, имя дизайна “design_1”, нажимаем ОК.

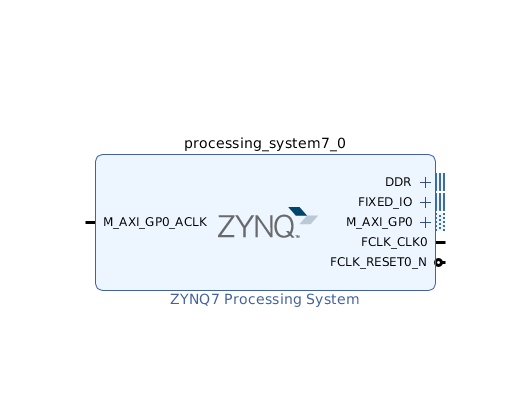

9. Нажимаем на “+” и добавляем ZYNQ7 Processing System

10. Меню поиска нужного IP.

11. Двойной клик по zynq ip, и выбираем presets (пред установки). Загрузить файл можно по ссылке (после скачивания файла, изменить расширение файла на tcl).

12. Выбираем z-turn-lite.tcl нажав предварительно применить конфигурацию (apply configuration …) в меню.

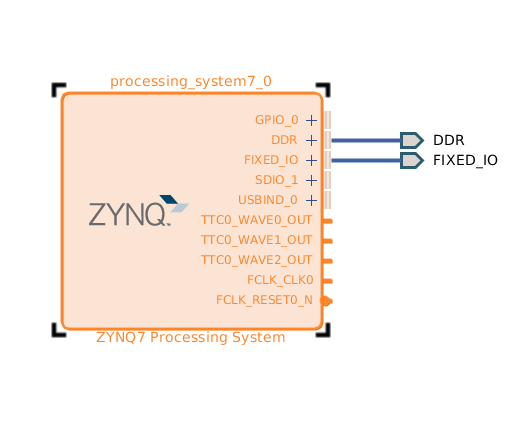

13. Нажимаем Run Block Automation. Появиться окно, в окне все настройки оставить по умолчанию.

14. Произошла конфигурация дизайна платы, настроились DDR3 временные характеристики, частоты процессора, сконфигурирована внешняя периферия.

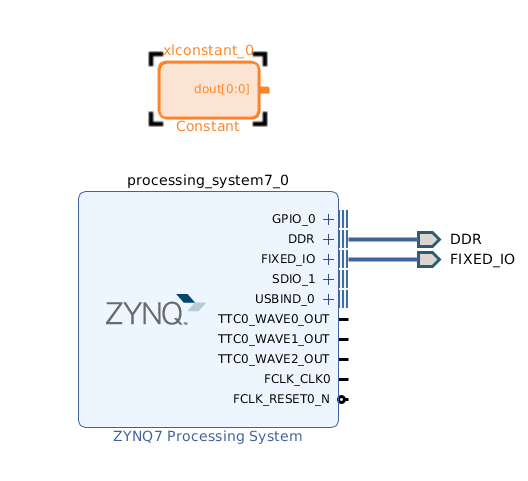

15. Добавляем IP блок константа.

16. Вводим значение константы 0. Нажимаем ОК.

17. Соединяем блок константы с блок zynq, как на рисунке выше.

18. Нажимаем правую кнопку мыши, выбираем “Generate Output Products …” и нажимаем кнопку “Генерировать”.

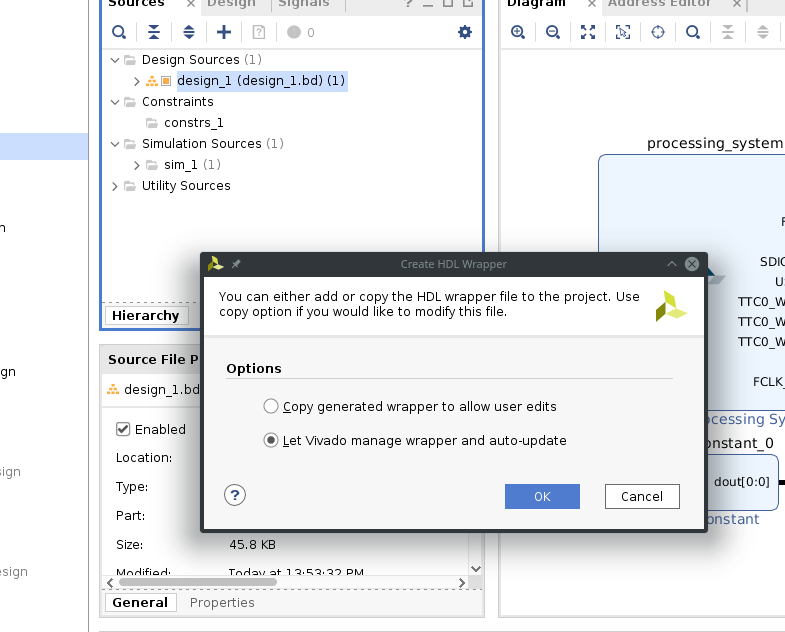

19. Нажимаем на “design_1” правой кнопкой мыши, выбираем “Create HDL Wrapper …”, нажимаем ОК.

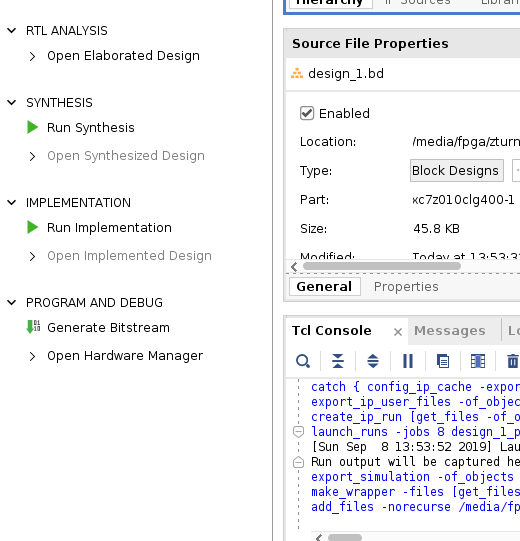

20. Подготовленный проект для создания bitstream (“прошивка плис”).

21. Нажимаем генерировать bitstream.

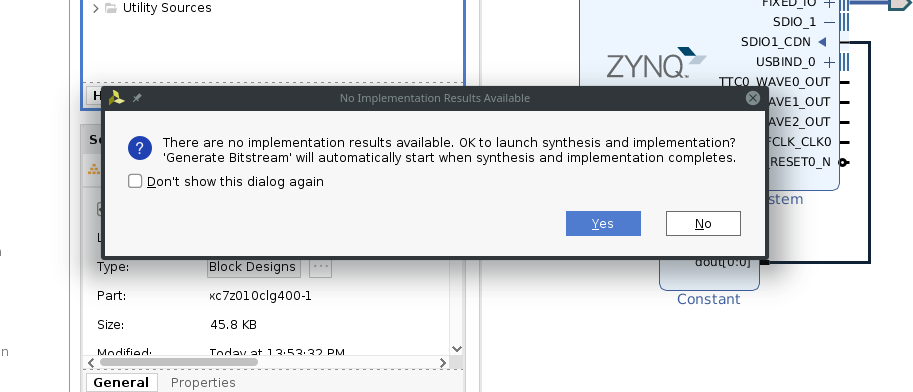

22. Нажимаем “Yes”.

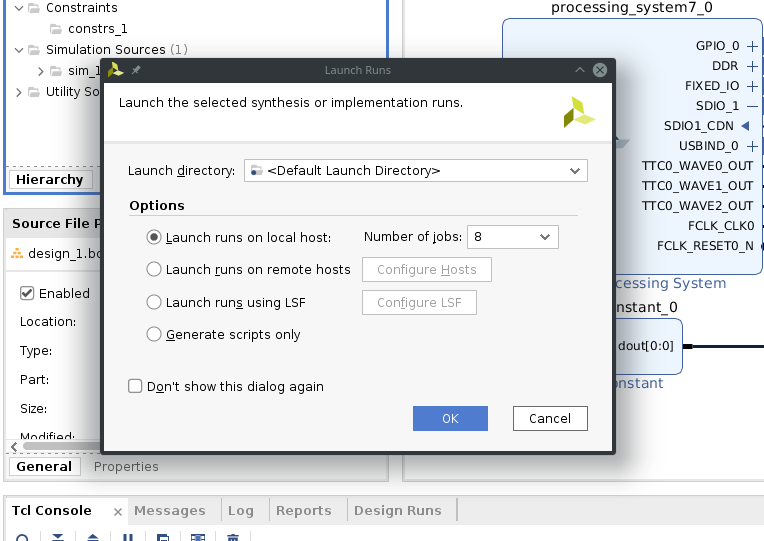

23. Выбираем, где и на какой машине собирать проект, цифра 8 количество ядер на ПК.

24. Нажимаем отменить.

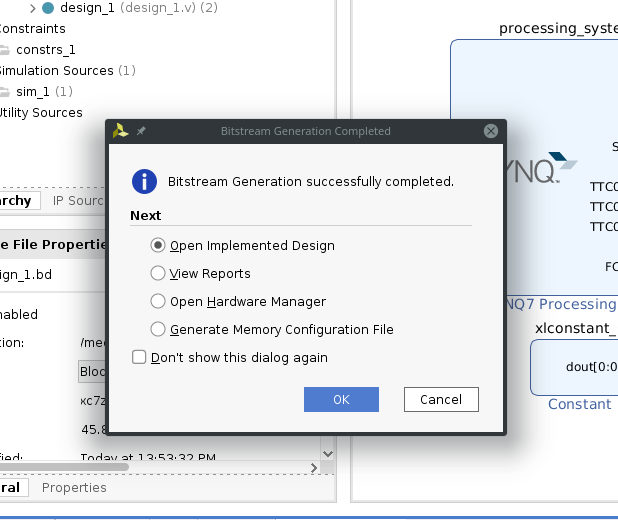

25. Делаем экспорт bitstream для Xilinx SDK (File > Export > Export Hardware).

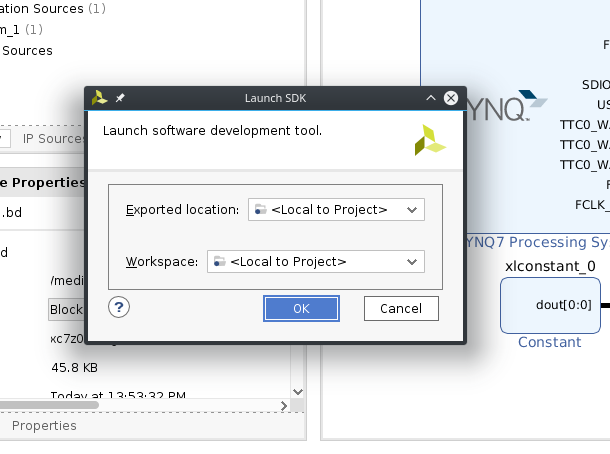

26. Запускаем SDK (File > Launch SDK).

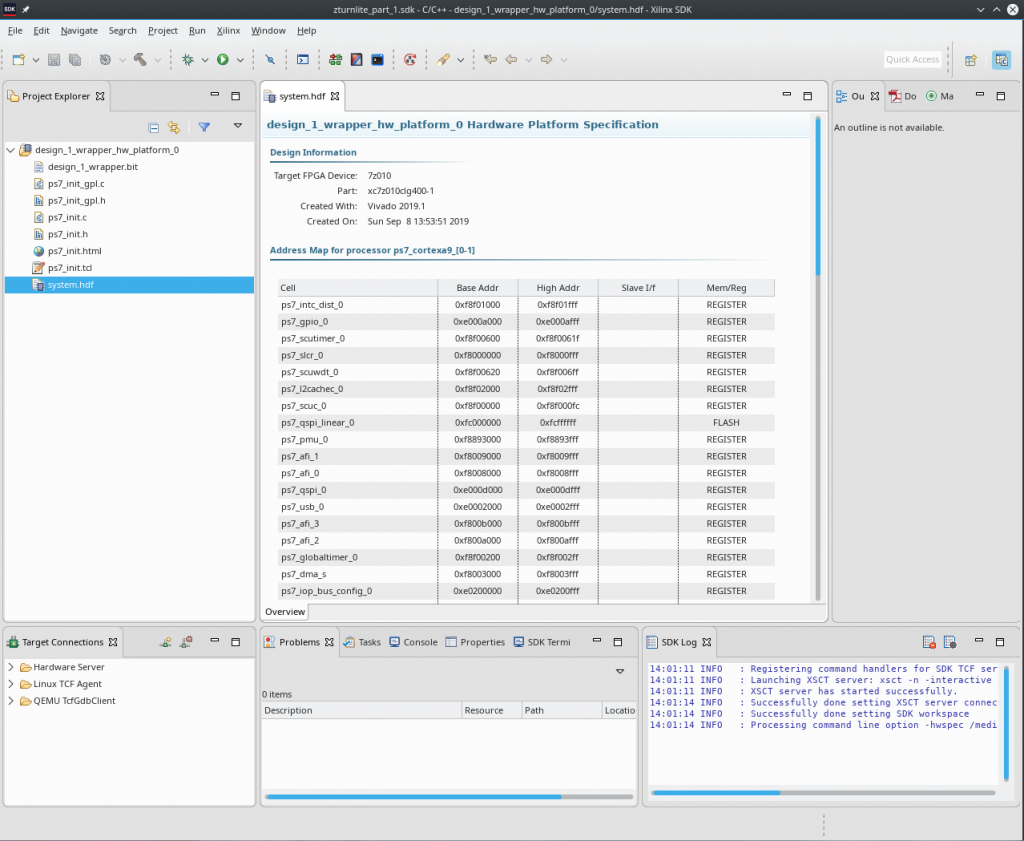

27. SDK содержит design_1_wrapper_hw_platform_0 (настройки для нашей платформы).

28. Проверяем подключен ли jtag ( у меня Platform Cable USB купленный на aliexpress)

29. Создаем проект по умолчанию, hello world помогать светодиодами на плате.

Демо проект

#include <stdio.h>

#include "xil_printf.h"

#include "xil_io.h"

#include "sleep.h"

int main()

{

print("PS_User_LED test\n\r");

Xil_Out32(0xE000A000 + 0x204,0x00000100);//set gpio8 as output

Xil_Out32(0xE000A000 + 0x208,0x00000100);//enable gpio8 output

while(1)

{

Xil_Out32(0xE000A000 + 0x00,0xFEFF0100);//gpio8 output value=1

sleep(1);

Xil_Out32(0xE000A000 + 0x00,0xFEFF0000);////gpio8 output value=0

sleep(1);

}

return 0;

}

Настройка jtag на linux (ubuntu 18.04):

Необходимо установить fxload, libusb, libusb-dev

sudo apt-get install fxload

sudo apt-get install libusb libusb-dev libusb-0.1-4

Копируем hex-файлы драйверов кабеля в /usr/share:

sudo cp “путь к XILINX”/Xilinx/Viavado/2019.1/data/xicom/*.hex /usr/share

Далее создаем файл /etc/udev/rules.d/52-xilinx-pcusb.rules

и заменяем все его содержимое на следующее:

# version 0003

SUBSYSTEM=="usb", ACTION=="add", ATTR{idVendor}=="03fd", ATTR{idProduct}=="0008", MODE:="666"

SUBSYSTEM=="usb", ACTION=="add", ATTR{idVendor}=="03fd", ATTR{idProduct}=="0007", MODE:="666"

SUBSYSTEM=="usb", ACTION=="add", ATTRS{idVendor}=="03fd", ATTRS{idProduct}=="0007", RUN+="/sbin/fxload -v -t fx2lp -I /usr/share/xusbdfwu.hex -D $tempnode"

SUBSYSTEM=="usb", ACTION=="add", ATTRS{idVendor}=="03fd", ATTRS{idProduct}=="0009", RUN+="/sbin/fxload -v -t fx2lp -I /usr/share/xusb_xup.hex -D $tempnode"

SUBSYSTEM=="usb", ACTION=="add", ATTRS{idVendor}=="03fd", ATTRS{idProduct}=="000d", RUN+="/sbin/fxload -v -t fx2lp -I /usr/share/xusb_emb.hex -D $tempnode"

SUBSYSTEM=="usb", ACTION=="add", ATTRS{idVendor}=="03fd", ATTRS{idProduct}=="000f", RUN+="/sbin/fxload -v -t fx2lp -I /usr/share/xusb_xlp.hex -D $tempnode"

SUBSYSTEM=="usb", ACTION=="add", ATTRS{idVendor}=="03fd", ATTRS{idProduct}=="0013", RUN+="/sbin/fxload -v -t fx2lp -I /usr/share/xusb_xp2.hex -D $tempnode"

SUBSYSTEM=="usb", ACTION=="add", ATTRS{idVendor}=="03fd", ATTRS{idProduct}=="0015", RUN+="/sbin/fxload -v -t fx2lp -I /usr/share/xusb_xse.hex -D $tempnode"

И последние шаги:

sudo chmod +x /etc/udev/rules.d/52-xilinx-pcusb.rules sudo udevadm control --reload-rules sudo udevadm trigger

Если прошло удачно загорится светодиод на jtag-е.