Тактирование и синхронизация – это основные элементы работы любого процессора (микроконтроллера и микропроцессора). Работа тактирования начинается с работы одного из следующих компонентов внутреннего или внешнего калибруемого RC-генератора, внешнего кварцевого резонатора или внешнего керамического резонатора. Тактирование: с сопровождением данных сигналами тактирования, с выработкой сигналов тактирования приемников. Проблема расфазирования тактовых импульсов для быстродействующих ЦПУ (центральное процессорное устройство) актуальна, что на современные БИС/СБИС (большие интегральные схемы/сверх большие интегральные схемы) устанавливают специальные модули, улучшающие синфазность тактовых сигналов в различных областях схем и при необходимости выполняющими и преобразования частоты (умножение, деление).

Для фазирования (коррекции) тактовых импульсов используют PLL (Phase Locked Loop), FLL (Frequency Locked Loop), DLL (Delay Locked Loop), DCM (Digital Clock Manager). Наибольшее распространение получила система фазовой автоподстройки частоты (ФАПЧ, PLL). Следует отметить, что PLL, по крайней мере, в реализуемых сейчас вариантах, – аналоговые устройства. Действительно, компенсируемый сдвиг фазы синхросигналов может иметь любое значение (является непрерывной величиной), поэтому и система его точной отработки должна работать в аналоговом режиме. С этой точки зрения PLL трудны для реализации. Являясь замкнутыми нелинейными системами, PLL могут оказаться неустойчивыми, что требует их для обеспечения надежной устойчивой работы во всем диапазоне изменения температуры и других воздействий.

Системы фазовой автоподстройки частоты представляют собой схемы с отрицательной обратной связью, которые состоят из генератора, управляемого напряжением (VCO) и фазового компаратора, которые включаются таким образом, что генератор поддерживает постоянный угол фазы по отношению к опорному сигналу. ФАПЧ может использоваться, например, для создания выходного сигнала со стабильной частотой из низкочастного сигнала фиксированной частоты.

В ФАПЧ сигнал рассогласования от фазового компаратора пропорционален разности фаз между сигналом на входе и сигналом вцепи обратной связи. Среднее значение сигнала на выходе фазового детектора будет оставаться постоянным в том случае, если входной сигнал в цепи обратной связи будет иметь одинаковую частоту.

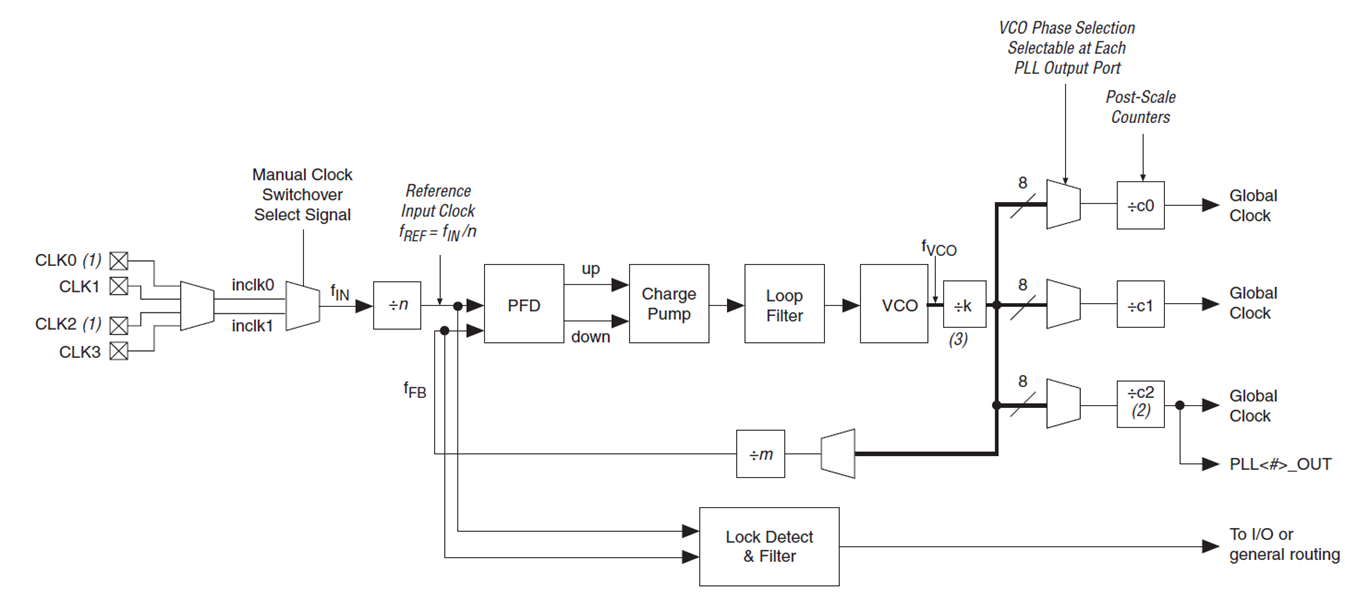

Базовая PLL архитектура (Altera Cyclone II)

Блок управления частотой (Altera Cyclone II)

Рассмотрим построение системы тактирования процессора на базе FPGA (Field-Programmable Gate Array – программируемая пользователем вентильная матрица) Altera Cyclone II EP2C5T144. Характеристика тактирования, данного FPGA: 2 области PLLs, 8 CLK выводов, 20 DPCLK выводов, 16 глобальных линий тактирования.

Каждый микроконтроллер имеет свою уникальную структуру внутреннего тактирования. Например, система тактирования STM32F756NGHx (ARM Cortex M7) имеет отдельные линии тактирования для LCD-TFT, USB и I2S. Внутренняя структура наполнения большим количеством делителей и умножителей, последнее является характерной чертой для AHB (Advanced High-performance Bus) – APB (Advanced Peripheral Bus) моста. AHB – APB – мост между шинами AHB и APB; используется для подключения различных APB – устройств, таких как компоненты отладки, к шине встроенных периферийных устройств процессора ARM. Кроме того, конструкция процессора позволяет производителям микросхем подключать дополнительные АРВ – устройства к внешней шине встроенных периферийных устройств (РРВ – Private Peripheral Bus) с помощью этой шины.Формирование спецификации системы тактирования разрабатывается на языках проектирования цифровой аппаратуры VHDL, Verilog, SystemVerilog. Далее создается функциональное описание работы системы тактирования для будущей микросхемы и происходит верификация. Современные микросхемы часто называются системами на кристалле (SoC) и содержат множество различных блоков, работающих параллельно и взаимодействующих между собой. Это сложное устройство, которое требует детальной проверки на правильность функционирования и отсутствие ошибок в проектном описании. Под проверкой подразумевается разработка детального плана и среды верификации на языке SystemVerilog c использованием методологии UVM (Universal Verification Methodology), её отладка, написание тестов, создание программной модели по спецификации, подготовка скриптов компиляции и запуска среды, скриптов анализа результатов множественных запусков. Верификация проекта цифровой интегральной схемы (ИС) — один из самых затратных по времени этапов разработки. Для достижения достаточной полноты проверки необходимо провести моделирование на большом наборе тестов и, если выявлены ошибки, после корректировки необходимо весь процесс моделирования повторить.

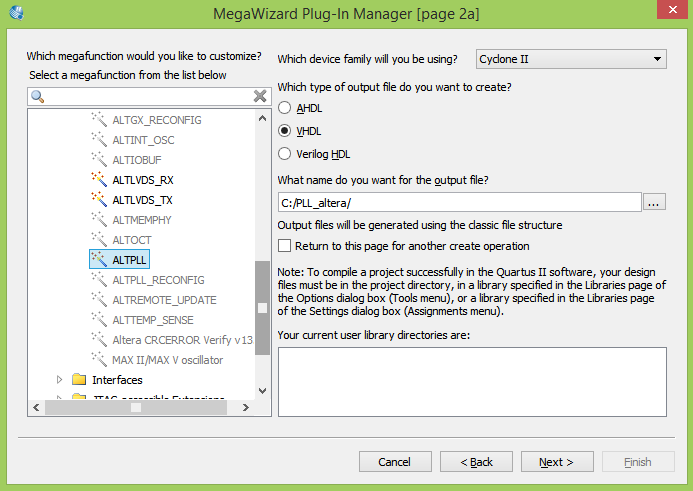

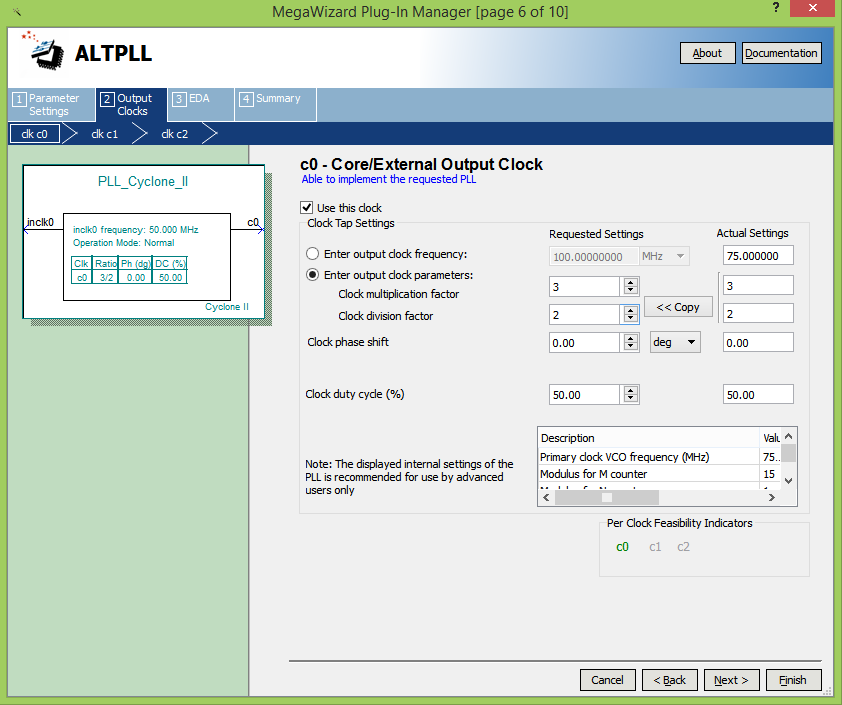

Формирование системы тактирования для архитектуры процессора произведем, используя Quartus II для FPGA и CPLD (complex Programmable Logic Device). Блок Altera Phase-Locked Loop (ALTPLL) использует внутренний PLL в связке с умножителями и делителями.

На вход PLL подается входная частота опорного генератора Fin. Далее на счетчике n опорная частота делится и получается иная частота Fref, которая поступает на фазовый детектор PFD (phase-frequency detector). Фазовый детектор сравнивает фазы частот Fref и той, что поступает с делителя m. Разность фаз, фильтруется и управляет генератором VCO. На выходе управляемого генератора – новая частота Fvco. Фазовый детектор подает управляющее воздействие на генератор VCO до тех пор, пока не выполнится условие Fref = Fvco/m. При этом условии частоты, подаваемые на детектор фаз равны. Таким образом, например, если m=2, то частота генератора VCO должна получиться в 2 раза выше частоты Fref. Последний этап – частота Fvco делится на выходном счетчике k. Подбирая коэффициенты n, m, k можно синтезировать довольно большой диапазон частот. Более сложные компоненты PLL позволяют перезагружать коэффициенты в процессе работы системы.

Блок Altera Phase-Locked Loop

LIBRARY ieee; USE ieee.std_logic_1164.all; LIBRARY altera_mf; USE altera_mf.all; ENTITY PLL IS PORT ( inclk0 : IN STD_LOGIC := '0'; c0 : OUT STD_LOGIC ); END PLL; ARCHITECTURE SYN OF pll IS SIGNAL sub_wire0 : STD_LOGIC_VECTOR (5 DOWNTO 0); SIGNAL sub_wire1 : STD_LOGIC ; SIGNAL sub_wire2 : STD_LOGIC ; SIGNAL sub_wire3 : STD_LOGIC_VECTOR (1 DOWNTO 0); SIGNAL sub_wire4_bv : BIT_VECTOR (0 DOWNTO 0); SIGNAL sub_wire4 : STD_LOGIC_VECTOR (0 DOWNTO 0); COMPONENT altpll GENERIC ( clk0_divide_by : NATURAL; clk0_duty_cycle : NATURAL; clk0_multiply_by : NATURAL; clk0_phase_shift : STRING; compensate_clock : STRING; inclk0_input_frequency : NATURAL; intended_device_family : STRING; lpm_hint : STRING; lpm_type : STRING; operation_mode : STRING; port_activeclock : STRING; port_areset : STRING; port_clkbad0 : STRING; port_clkbad1 : STRING; port_clkloss : STRING; port_clkswitch : STRING; port_configupdate : STRING; port_fbin : STRING; port_inclk0 : STRING; port_inclk1 : STRING; port_locked : STRING; port_pfdena : STRING; port_phasecounterselect : STRING; port_phasedone : STRING; port_phasestep : STRING; port_phaseupdown : STRING; port_pllena : STRING; port_scanaclr : STRING; port_scanclk : STRING; port_scanclkena : STRING; port_scandata : STRING; port_scandataout : STRING; port_scandone : STRING; port_scanread : STRING; port_scanwrite : STRING; port_clk0 : STRING; port_clk1 : STRING; port_clk2 : STRING; port_clk3 : STRING; port_clk4 : STRING; port_clk5 : STRING; port_clkena0 : STRING; port_clkena1 : STRING; port_clkena2 : STRING; port_clkena3 : STRING; port_clkena4 : STRING; port_clkena5 : STRING; port_extclk0 : STRING; port_extclk1 : STRING; port_extclk2 : STRING; port_extclk3 : STRING ); PORT ( clk : OUT STD_LOGIC_VECTOR (5 DOWNTO 0); inclk : IN STD_LOGIC_VECTOR (1 DOWNTO 0) ); END COMPONENT; BEGIN sub_wire4_bv(0 DOWNTO 0) <= "0"; sub_wire4 <= To_stdlogicvector(sub_wire4_bv); sub_wire1 <= sub_wire0(0); c0 <= sub_wire1; sub_wire2 <= inclk0; sub_wire3 <= sub_wire4(0 DOWNTO 0) & sub_wire2; altpll_component : altpll GENERIC MAP ( clk0_divide_by => 3, clk0_duty_cycle => 50, clk0_multiply_by => 2, clk0_phase_shift => "0", compensate_clock => "CLK0", inclk0_input_frequency => 20000, intended_device_family => "Cyclone II", lpm_hint => "CBX_MODULE_PREFIX=PLL", lpm_type => "altpll", operation_mode => "NORMAL", port_activeclock => "PORT_UNUSED", port_areset => "PORT_UNUSED", port_clkbad0 => "PORT_UNUSED", port_clkbad1 => "PORT_UNUSED", port_clkloss => "PORT_UNUSED", port_clkswitch => "PORT_UNUSED", port_configupdate => "PORT_UNUSED", port_fbin => "PORT_UNUSED", port_inclk0 => "PORT_USED", port_inclk1 => "PORT_UNUSED", port_locked => "PORT_UNUSED", port_pfdena => "PORT_UNUSED", port_phasecounterselect => "PORT_UNUSED", port_phasedone => "PORT_UNUSED", port_phasestep => "PORT_UNUSED", port_phaseupdown => "PORT_UNUSED", port_pllena => "PORT_UNUSED", port_scanaclr => "PORT_UNUSED", port_scanclk => "PORT_UNUSED", port_scanclkena => "PORT_UNUSED", port_scandata => "PORT_UNUSED", port_scandataout => "PORT_UNUSED", port_scandone => "PORT_UNUSED", port_scanread => "PORT_UNUSED", port_scanwrite => "PORT_UNUSED", port_clk0 => "PORT_USED", port_clk1 => "PORT_UNUSED", port_clk2 => "PORT_UNUSED", port_clk3 => "PORT_UNUSED", port_clk4 => "PORT_UNUSED", port_clk5 => "PORT_UNUSED", port_clkena0 => "PORT_UNUSED", port_clkena1 => "PORT_UNUSED", port_clkena2 => "PORT_UNUSED", port_clkena3 => "PORT_UNUSED", port_clkena4 => "PORT_UNUSED", port_clkena5 => "PORT_UNUSED", port_extclk0 => "PORT_UNUSED", port_extclk1 => "PORT_UNUSED", port_extclk2 => "PORT_UNUSED", port_extclk3 => "PORT_UNUSED" ) PORT MAP ( inclk => sub_wire3, clk => sub_wire0 ); END SYN;

Созданный блок тактирования является основой работы любой архитектуры процессора, дальнейшие формирование частоты реализуется для работы внутренних шин процессора и внутренней периферии (UART/USART, SPI, I2C, SDIO и др.)

One thought on “Тактирование, синхронизация и ФАПЧ процессора”

Thank you for your forum topic.Much thanks again. Awesome. Zell

Comments are closed.