Думаю, пришло время начать писать про ПЛИСины (FPGA). “Первая ласточка” – проекты дающие начальные сведения о том, как начать писать на VHDL и “пилить” FPGA, и конечно многое другое. Программируемая логическая интегральная схема (ПЛИС) — электронный компонент, используемый для создания цифровых интегральных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования, все таки более правильно описания). Для программирования используются программаторы и отладочные среды, позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или программы на специальных языках описания аппаратуры: Verilog, VHDL, AHDL и др. Если хотите стать большим гиком в этой области, то советую уже сейчас начать учить цифровую схемотехнику. А как же я пришел к этому, к описанию для FPGA? В один прекрасный день листая очередное руководство на 1500 страниц по ARM-ам, понял пара что-то с этим делать, пара делать свои структуры, пара делать девайсы на языке задачи, на языке цифровой “схемоты”. Первое что вам понадобится это FPGA или CPLD матрица, у меня FPGA матрица Cyclone II EP2C5T144, ее можно приобрести на китайском интернет магазине aliexpress.com или dx.com, плюс нам нужен программатор для этой штуковины (Altera USB – Blaster).

Сначала качаем программу quartus II и устанавливаем ее (у меня версия 13sp1, она подходит под моего железа).

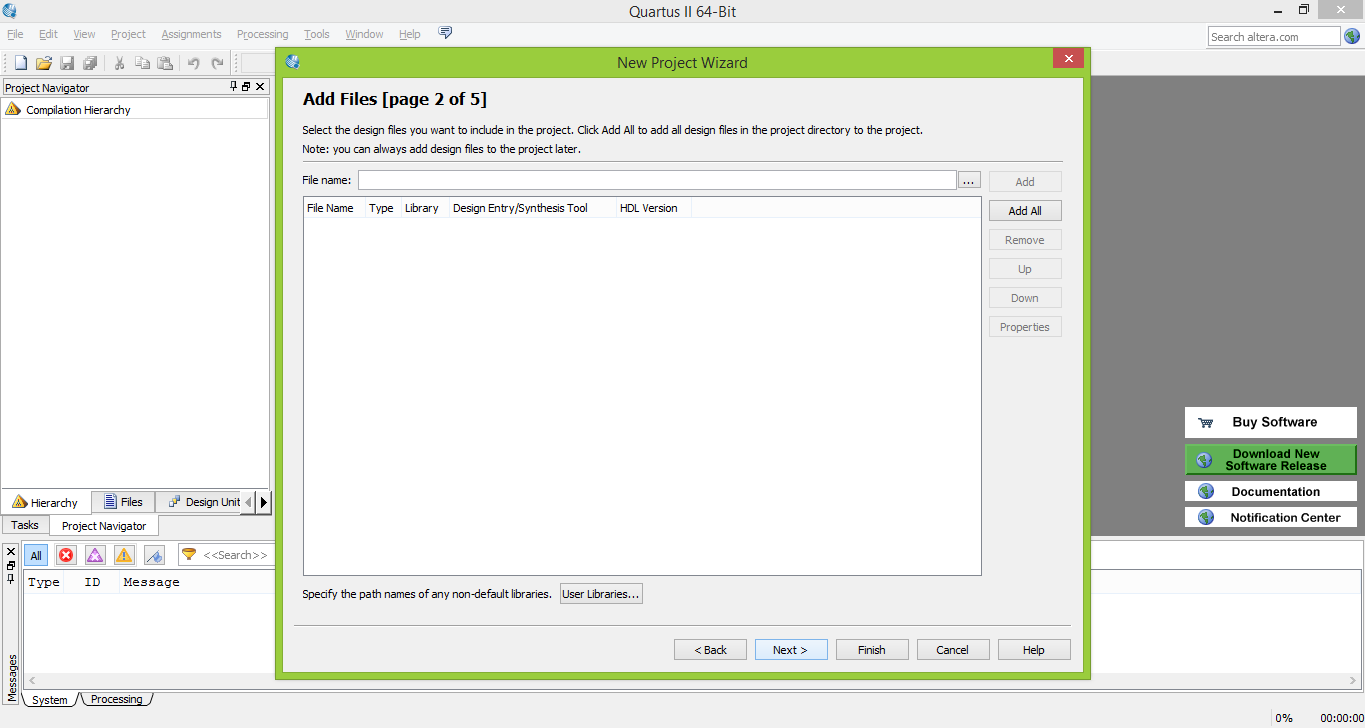

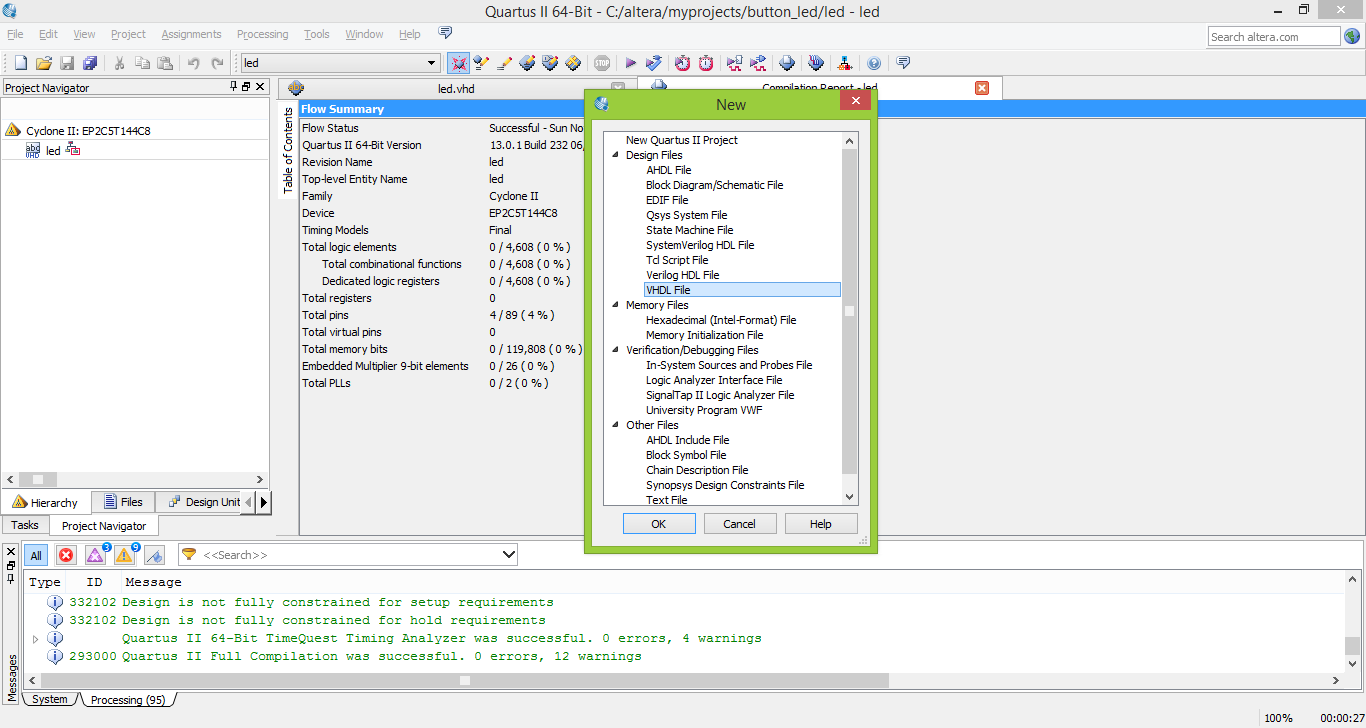

Процесс создания проекта.

1-ый пример. При нажатии на кнопку загораются светодиоды (схема).

library IEEE; use IEEE.STD_LOGIC_1164.all; entity pr1 is port ( BUTTON_PUSH1_PIN144 : in std_ulogic; LED_D2_PIN3 : out std_ulogic; LED_D4_PIN7 : out std_ulogic; LED_D5_PIN9 : out std_ulogic ); end pr1; architecture led_architecture of pr1 is begin process (BUTTON_PUSH1_PIN144) begin LED_D2_PIN3 <= BUTTON_PUSH1_PIN144; LED_D4_PIN7 <= BUTTON_PUSH1_PIN144; LED_D5_PIN9 <= BUTTON_PUSH1_PIN144; end process; end led_architecture;

led_plus_button.7z – исходник проекта.

2-ой пример. Используя внешний кварцевый генератор тактируем ножку, считаем количество тактов, чтобы количество было пропорционально 1 секунде, тем самым мигаем светодиодам.

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity pr5 is port (clk : in std_logic; led : out std_logic); end pr5; architecture my_architecture of pr5 is signal signalVariable : std_logic_vector (26 downto 0) := "000000000000000000000000000"; constant constantOne : std_logic_vector (26 downto 0) := "000000000000000000000000001"; begin process (clk) begin if(clk = '1' and clk'event) then signalVariable <= std_logic_vector(unsigned(signalVariable) + unsigned(constantOne)); if signalVariable = "010111110101111000010000000" then led <= '1'; end if; if signalVariable = "101111101011110000100000000" then led <= '0'; signalVariable <= "000000000000000000000000000"; end if; end if; end process; end my_architecture;

blink_led.7z – исходник проекта.

Структура описаний схем на VHDL.

Описание схемы включает две части.

Первая часть – описание схемы, как компонента некоторой надсистемы, т.е. это, в основном, описание интерфейсов схемы с внешней средой. Вид этой части, называемой сущностью:

entity имя_сущности is

декларации;

end имя_сущности;

Назначение второй части – описание внутренних свойств схемы (структуры или функций), она называется архитектурным телом:

architecture имя_ахитектурного_тела of имя_сущности is

[декларации;]

begin

описание_схемы_или_алгоритма;

end имя_архитектурного_тела;

У одной схемы (сущности) может быть несколько архитектурных тел, так как могут быть описаны разные аспекты (структура или алгоритмы) и версии объекта, причем на разных иерархических уровнях.

Процессы.

Моделирование в VHDL осуществляется событийным методом. Реализуется этот метод, благодаря не только учету задержек, но и специальным механизмам таким, как оператор process или охраняемые блоки. Рrocess – это блок, выполняемый только тогда, когда происходят изменения его входных параметров. Структура этого блока:

[метка:] process [(список параметров)]

тело_процесса; — здесь описываются вложенные в процесс типы и операторы

end process [метка];

Охраняемый (guarded) блок имеет вид:

метка: block (охранное_выражение) begin операторы end block метка;

Операторы блока выполняются только при истинном значении охранного выражения.

Сигналы — это объекты, значения которых могут меняться и которые имеют временные параметры. Сигналы соответствуют физическим линиям (проводникам), которые соединяют элементы схемы. Для объявления сигнала используется оператор signal, за ним через пробел следует одно или через запятую несколько имен (идентификаторов) сигналов, двоеточие и тип сигнала.

Для начала хватит, продолжим следующий раз.